Parallel Data Architectures & Brain Computer Interface Group.

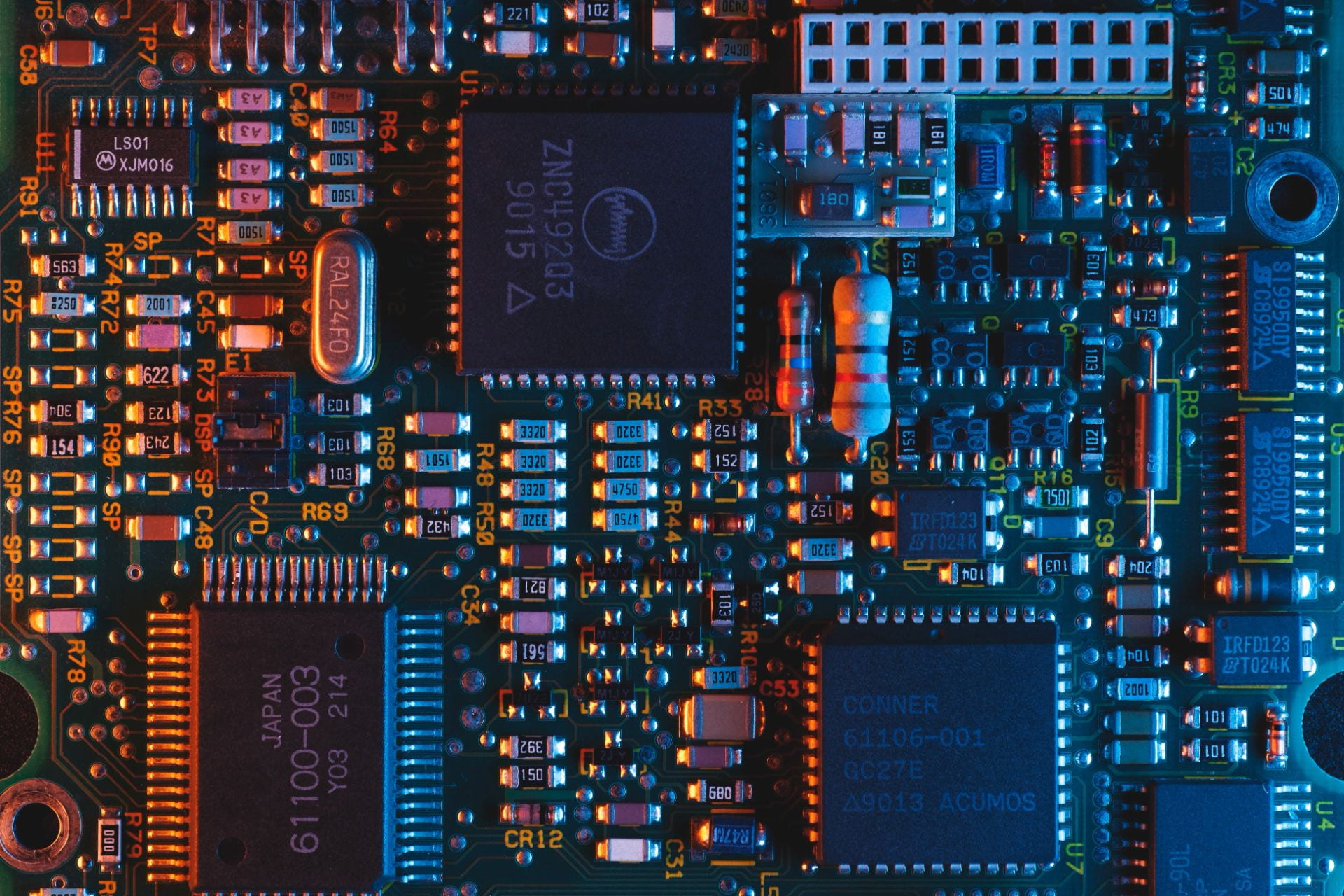

Efficient System and Devices

Neuroscience Applications

Donec iaculis gravida semper. Etiam ullamcorper mauris nec augue elementum, id vestibulum urna elementum. Class aptent taciti sociosqu ad litora torquent per conubia nostra, per inceptos himenaeos. Aliquam nec bibendum lorem, sed ultricies massa. Nam at ante urna. Nullam sollicitudin nec diam vitae mattis. Nullam id porta dui, id venenatis dui.

Cras scelerisque augue tristique sem finibus tempus. Donec rhoncus ut neque eu gravida. Nullam orci ipsum, eleifend vel aliquam vulputate, eleifend vel tortor. Etiam porttitor ligula nisl, quis pharetra libero sollicitudin ac. Integer eleifend faucibus nulla, eu tempor urna elementum placerat. Aenean tortor augue, efficitur sed purus ac, pellentesque ornare tortor. Sed ornare dui tortor, pretium vehicula sem accumsan a. Maecenas fringilla maximus diam, quis sagittis turpis faucibus vel. Nunc ultrices, est id rhoncus molestie, urna risus faucibus enim, a sagittis lacus ex sed dolor. Curabitur lacus enim, tincidunt sit amet erat non, semper suscipit quam.